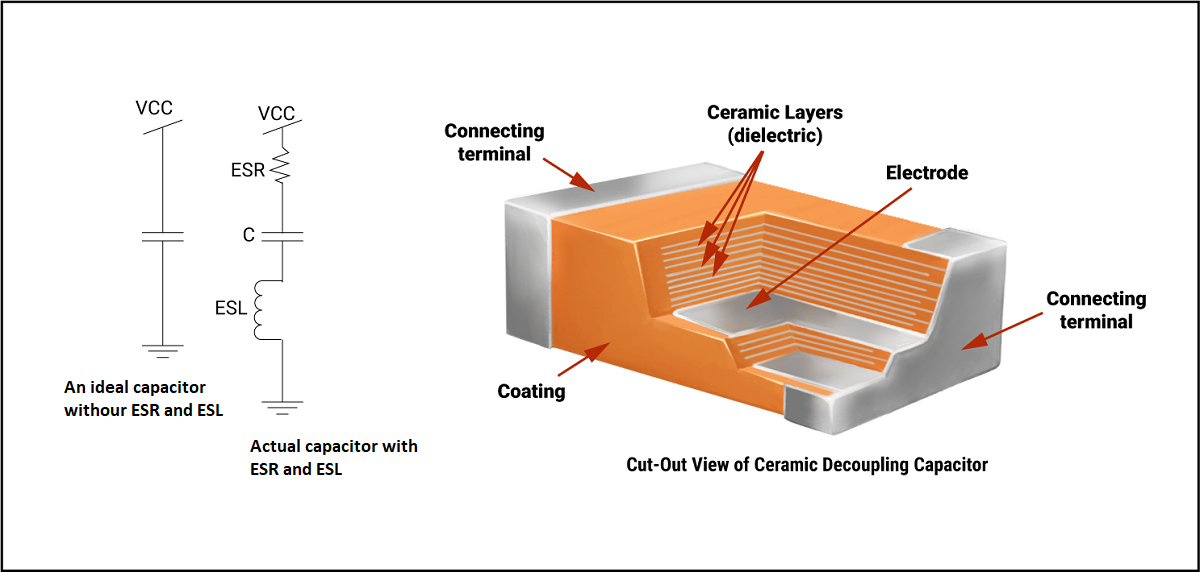

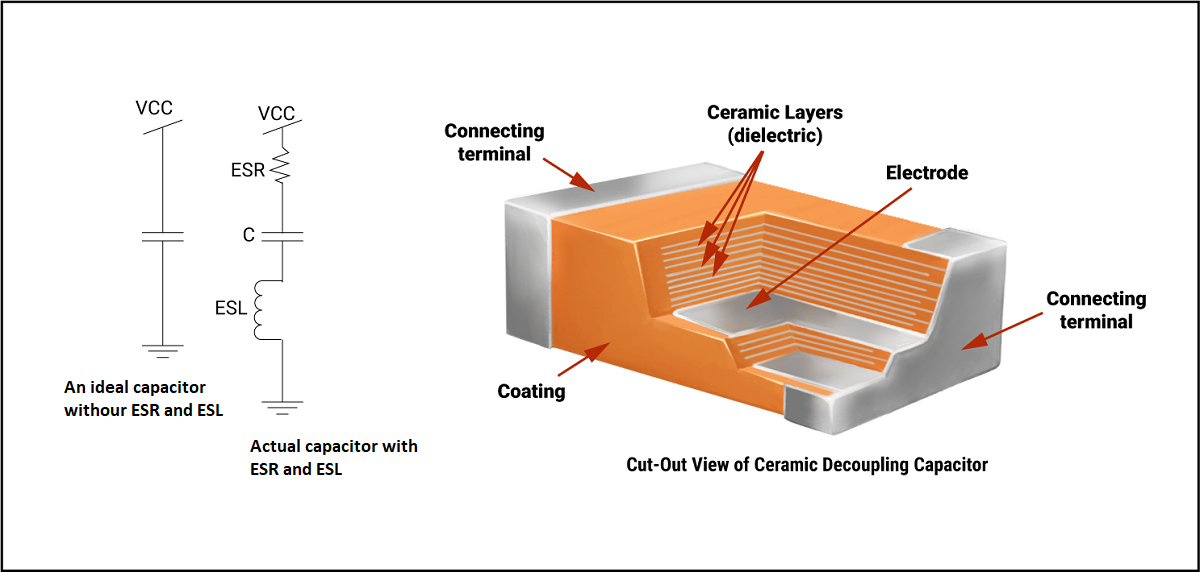

WHAT IS PROPER DECOUPLING AND WHY IS IT NECESSARY? Most ICs suffer performance degradation of some type if there is ripple and/or noise on the power supply pins. A digital IC will incur a reduction in its noise margin and a possible increase in clock jitter. In electronics, a decoupling capacitor is a capacitor used to decouple (i.e. prevent electrical energy from transferring to) one part of a circuit from another. Noise caused by other circuit elements is shunted through the capacitor, reducing its effect on the rest of the circuit.

PCB Layout Guidelines for Decoupling and Bypassing Capacitors OnElectronTech

First, consider decoupling capacitors. It is generally stated that the purpose of PCB decoupling capacitor placement is to ensure the voltage between the power rail/plane and the ground plane remains constant against low-frequency power supply noise, ringing on the PDN, and any other voltage fluctuations on the PDN. Learn about what a decoupling capacitor is. Understand why decoupling capacitor placement matters. Find out how to place decoupling capacitors correctly. A decoupling capacitor stabilizes voltage for ICs. I'm a true Ikea fan at heart. Decoupling capacitors are used for power supply and transient decoupling because of their intrinsic energy storage capability. Complex PCB assemblies have multiple power supplies that require voltage regulation to ensure the proper operation of components such as processors, FPGAs, ICs, or amplifiers. What Does a Decoupling Capacitor Actually Do? Methods for Sizing Decoupling Capacitors Estimating Total Decoupling Capacitance Based on Charging Up Traces Simple Example: A Digital IC With 12 Outputs Are these decoupling capacitors sized properly?

Pcb Layout Decoupling Capacitors Claire Trend

To download the project files referred to in this video visit:http://www.keysight.com/find/eesof-how-to-decapTo apply for a free trial of ADS visit:http://ww. Power supply noise management continues to be a challenge with the scaling of CMOS technologies. Use of on-chip decoupling capacitors (decaps) is the most common noise suppression technique and has significant associated area and leakage costs. There are numerous methods of implementing decaps and it is not always clear which implementation is the most optimal for the given design constraints. With the ever-increasing integration density of electronic systems and reduced noise margins, maintaining high power integrity has become a formidable challenge in the design of high-performance 3D integrated circuits (3D ICs). To enhance power integrity, the insertion of decoupling capacitors has proven to be an important and effective solution. However, existing decoupling capacitor. Decoupling capacitors are used to filter out voltage spikes and pass through only the DC component of the signal. The idea is to use a capacitor in such a way that it shunts, or absorbs the noise making the DC signal as smooth as possible.

Decoupling Capacitor Placement Guidelines Sierra Circuits

4.2 nRF52840 capacitor selection. In the schematic design for the application, it is important to select decoupling capacitors with sufficient efficient capacitance for decoupling. When designing the decoupling of the nRF52840 device, the following must be considered. Low voltage (LV) mode - DEC4 decoupling. Decoupling Capacitor Optimization to Achieve Target Impedance in PCB PDN Design Abstract: With increasingly stringent requirements for lower voltage supply, and higher density in PCB (Printed Circuit) PDN (Power Distribution Network) design, power integrity has an increasingly important role in PCB design. The PI performance of the PCB design must meet requirements, or modification and trial.

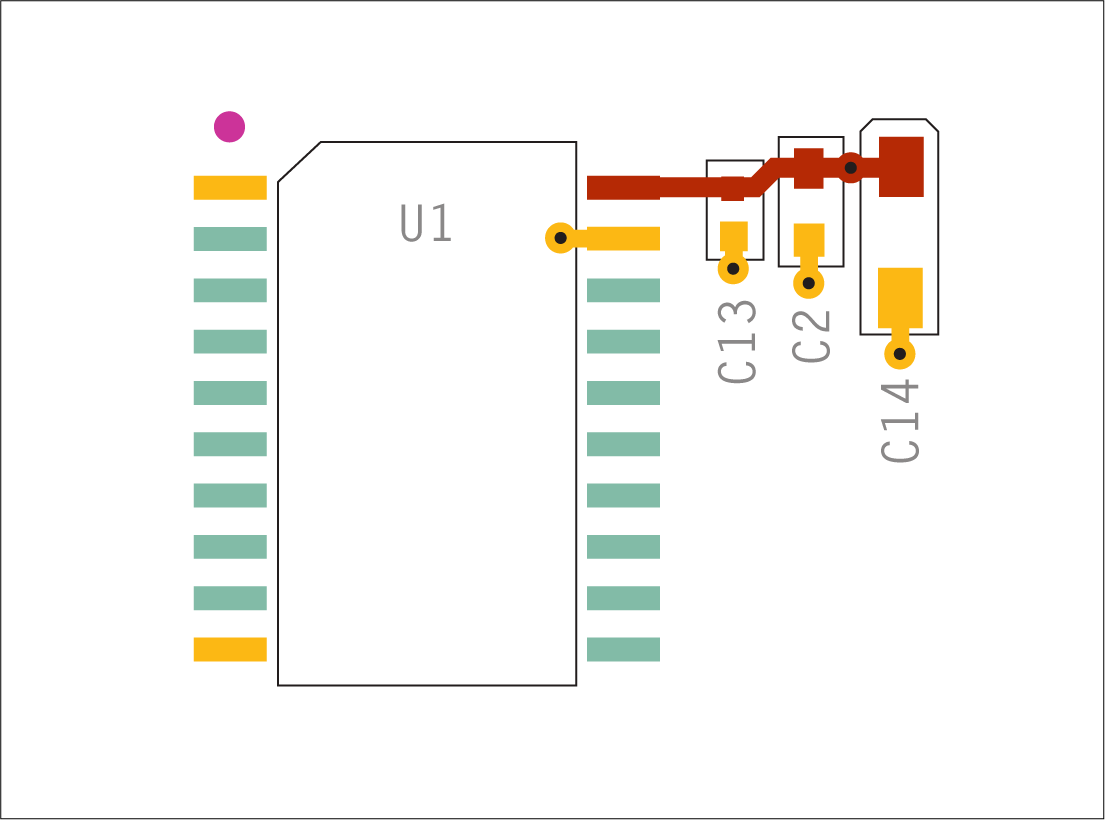

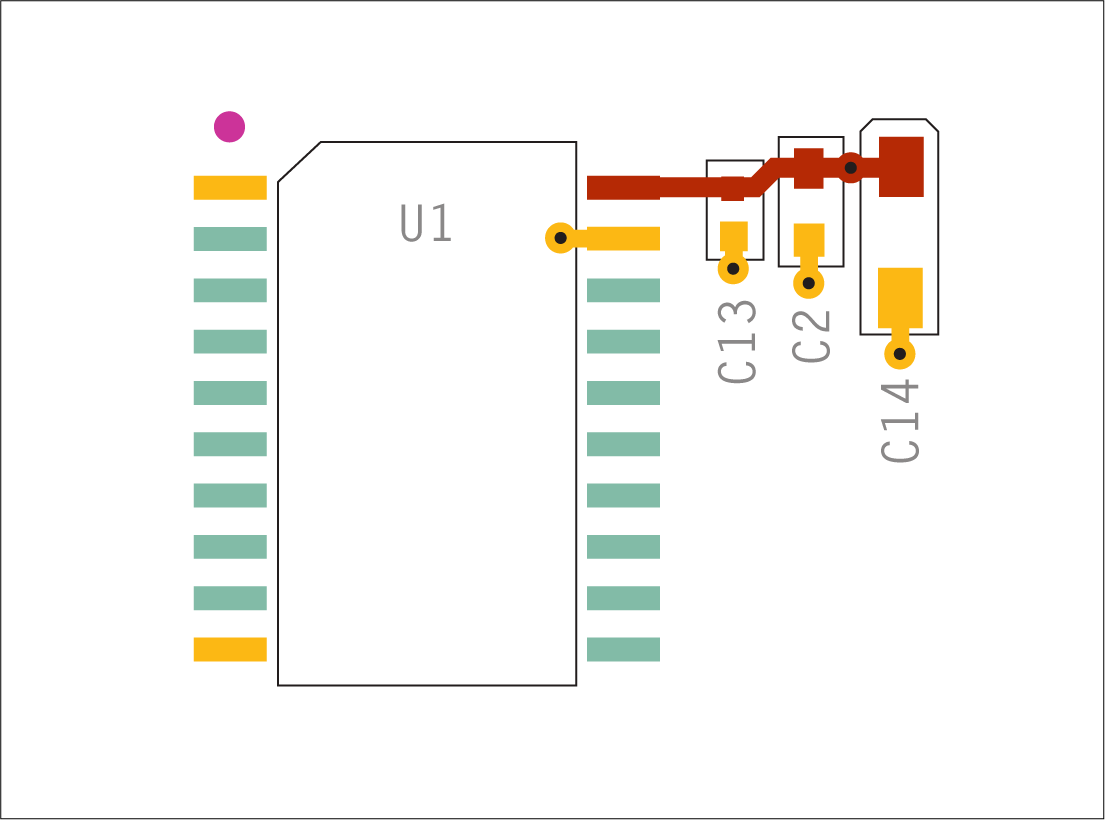

From a circuit model standpoint, decoupling capacitor optimization targets points 2 and 3, and you'll need to balance the number of capacitors you use with the total capacitance required at a given self-resonant frequency. Analog SPICE simulations are great tools to help you design the impedance of a decoupling network. ABSTRACT Much research has been done on decoupling capacitor selection and placement for BGAs. This application report provides the current best practices, and what TI recommends in general for placement and selection of values. In the past, TI (and many other semiconductor companies) recommended 1 capacitor (cap) per power pin.

What is the Use of a Decoupling Capacitor? Sierra Circuits

Decoupling capacitors help to isolate, or de-couple, local circuits from noise and power anomalies from other devices on shared power, ground, and other nets. They are typically applied to power sources to provide a localized source of instantaneous current and provide isolation of the local circuit from power noise in other areas of the design. Board Decoupling Capacitors Guide. 3.1. Board Decoupling Capacitors Guide. In addition to OPD (as LSC and DSC), the Intel® Agilex™ device family also offers a cavity site or state to place large size back side capacitors as close as possible to the die or package to improve transient voltage droop response and reduce second or third voltage.