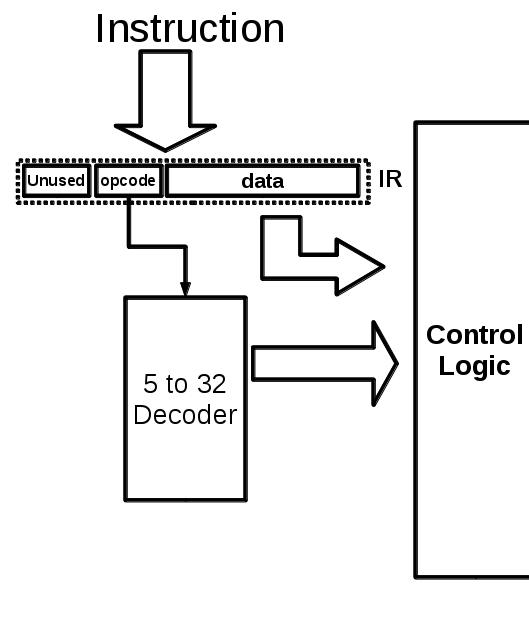

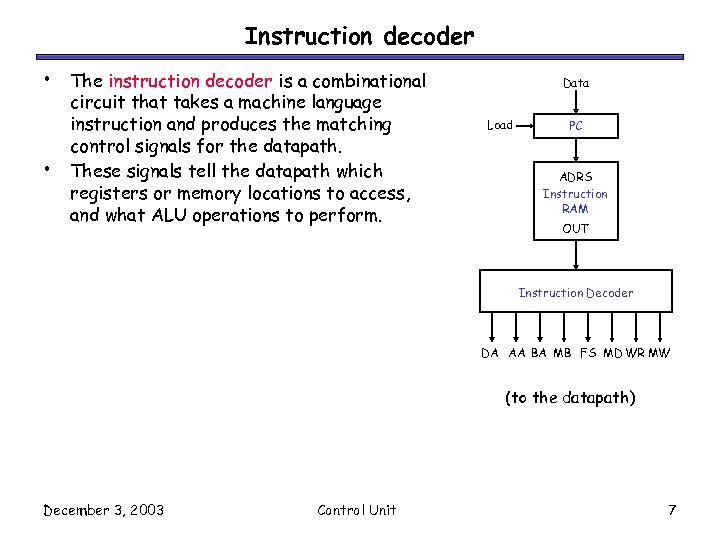

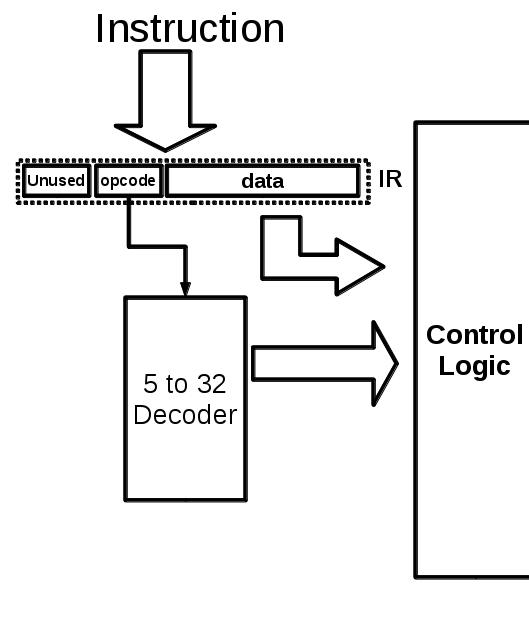

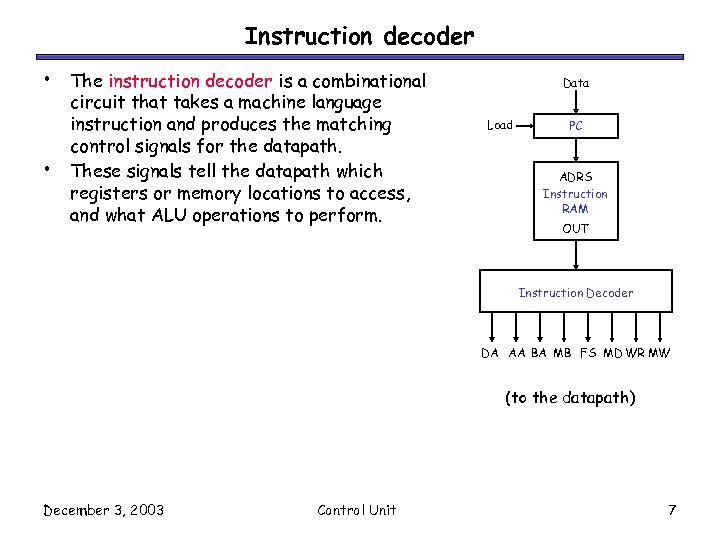

The instruction decoder logic converts the op-code bits into settings for all the internal control lines. The operand provides a literal, file register address or program address, which will be used by the instruction. The Instruction Decoder reads the next instruction in from memory, and sends the component pieces of that instruction to the necessary destinations. For each machine-language instruction, the control unit produces the sequence of pulses on each control signal line required to implement that instruction (and to fetch the next instruction).

Decoder

1. Encoders - An encoder is a combinational circuit that converts binary information in the form of a 2 N input lines into N output lines, which represent N bit code for the input. For simple encoders, it is assumed that only one input line is active at a time. As an example, let's consider Octal to Binary encoder. An instruction decoder takes in an instruction and outputs all of the control signals for that instruction. The other way to do it is to use ROM control. Every instruction implemented by a processor maps to an address in a Read-Only Memory (ROM) unit.. The main CPU circuit (located in cpu.circ) implements the main datapath and connects all. Decoder is a combinational circuit that has 'n' input lines and maximum of 2 n output lines. One of these outputs will be active High based on the combination of inputs present, when the decoder is enabled. That means decoder detects a particular code. An alternate circuit for the 2-to-4 line decoder is: Replacing the 1-to-2 Decoders with their circuits will show that both circuits are equivalent. In a similar fashion a 3-to-8 line decoder can be made from a 1-to-2 line decoder and a 2-to-4 line decoder, and a 4-to-16 line decoder can be made from two 2-to-4 line decoders.

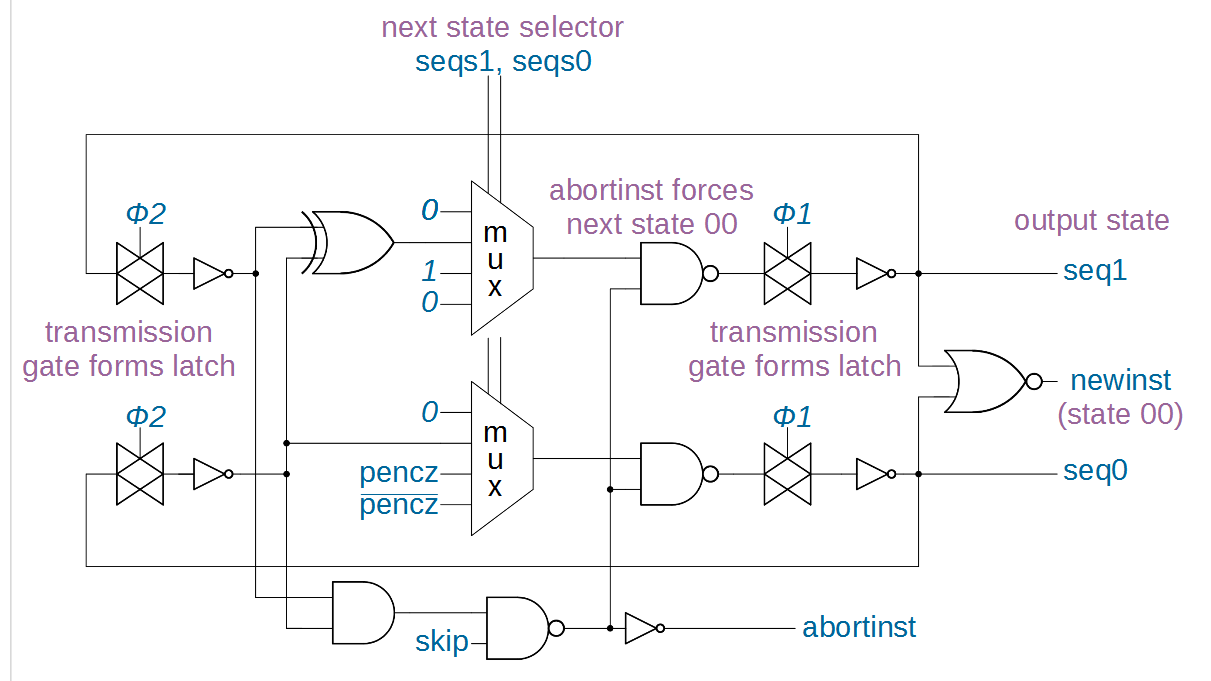

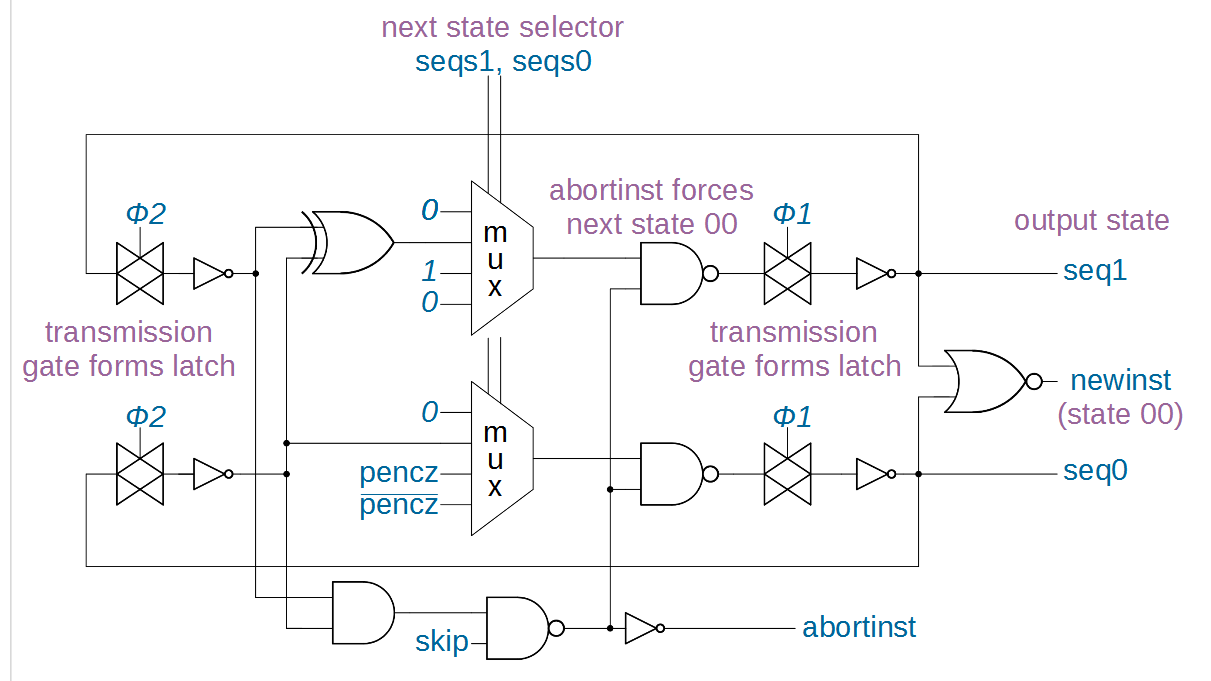

Reverse engineering ARM1 instruction sequencing, compared with the Z80

The instruction decoder is the circuit that decodes an opcode. As an example, on the 6502 CPU, the opcode for the CLI (clear interrupt) instruction is 01011000 in binary. The CPU receives this as a set of digital logic signals on the data bus. How does it go from getting these signals to executing the procedure for the CLI instruction? 1. Exercise the complete CPU designed by last year's CS220 class. 2. Design the circuits for each of the pins on the Instruction Decoder. 3. Implement the Instruction Decoder. 4. Turn in the items described in Part 4. Part 1: Exercise the Complete CPU Drag the file MINIJVMFINAL.cct to the desktop, start up LogicWorks, and open this file. The instruction decoder of a processor is a combinatorial circuit sometimes in the form of a read-only memory, sometimes in the form of an ordinary combinatorial circuit. Its purpose is to translate an instruction code into the address in the micro memory where the micro code for the instruction starts. The state machine within CPU is the instruction decoder.https://www.iklearn.com

Instruction Decoder

An Instruction Decoder is a circuit that processors implement in order to interpret instructions coming from memory. In synchronous designs, this circuit feeds the appropriate operands into the datapath of the processor, according to the instruction. Additionally, it must communicate with a Controller, whose role is to direct the flow of the. The execution of an instruction in a standard digital computer occurs in three or four phases: Fetching the instruction from main memory or cache memory into the instruction register in the CPU. Decoding the instruction and generation of the data operand address (as in the case of a LOAD or a STORE instruction)

Decoder •A decoder with i inputs and fully-populated outputs has 2 i outputs •It is generally better to work with both the input and output as buses rather than individual signals •Output is "one-hot" - One and only one output is high at a time •Common uses: - Selection of a word within a memory - Selection of one module A decoder is a logic circuit that converts a coded input to a "decoded" output by converting the input into a different format. Binary decoders can be used to: Convert BCD/binary value into "denary format", "octal format" or "hexadecimal format", Decoding the opcode of an instruction (Decode stage of the FDE Cycle). One of the.

Control units In the last

Basic Principe of Decoder: As told earlier, the decoder is just a counter part of an Encoder. It takes a particular number of binary values as inputs and decodes then into more lines by using logic. A sample decoder is shown below which takes in 2 Lines as input and converts them to 4 Lines. Instruction decoder: 4. Evaluate Operand Address Phase Compute address of the memory location of the instruction operand. Memory Circuitry: 5. Fetch Operands Phase Load MAR with address. Simple circuits, such as an adder, wired together, are part of the microcode.